Uvod u LED drajver čip

sa brzim razvojem industrije automobilske elektronike, LED drajver čipovi visoke gustine sa širokim rasponom ulaznog napona se široko koriste u automobilskoj rasvjeti, uključujući vanjsko prednje i stražnje osvjetljenje, unutrašnje osvjetljenje i pozadinsko osvjetljenje ekrana.

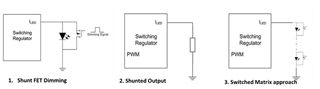

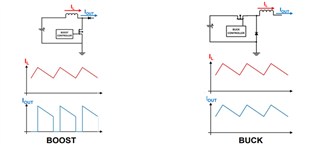

LED drajver čipovi se mogu podeliti na analogno zatamnjivanje i PWM zatamnjenje prema metodi zatamnjivanja.Analogno zatamnjivanje je relativno jednostavno, PWM zatamnjivanje je relativno složeno, ali raspon linearnog zatamnjivanja je veći od analognog zatamnjivanja.LED drajver čip kao klasa čipa za upravljanje napajanjem, čija je topologija uglavnom Buck i Boost.Neprekidna izlazna struja kola je kontinuirana tako da je njeno talasanje izlazne struje manje, što zahtijeva manji izlazni kapacitet, pogodnije za postizanje velike gustine snage kola.

Slika 1 Pojačavanje izlazne struje u odnosu na smanjenje

Slika 1 Pojačavanje izlazne struje u odnosu na smanjenje

Uobičajeni načini kontrole LED drajver čipova su trenutni režim (CM), COFT (kontrolisano vreme isključenja) režim, COFT & PCM (režim vršne struje).U poređenju sa trenutnom kontrolom, COFT način upravljanja ne zahtijeva kompenzaciju petlje, što doprinosi poboljšanju gustine snage, uz brži dinamički odziv.

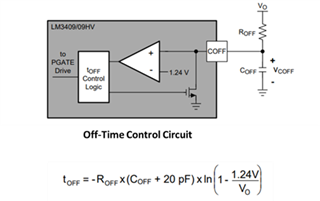

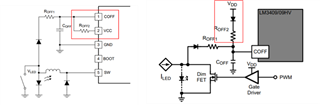

Za razliku od drugih načina upravljanja, čip načina kontrole COFT ima poseban COFF pin za podešavanje vremena isključenja.Ovaj članak predstavlja konfiguraciju i mjere predostrožnosti za eksterno kolo COFF-a zasnovano na tipičnom COFT-kontroliranom Buck LED upravljačkom čipu.

Osnovna konfiguracija COFF-a i mjere opreza

Princip upravljanja COFT režima je da kada struja induktora dostigne postavljeni nivo struje, gornja se cev isključuje, a donja se uključuje.Kada vrijeme isključenja dostigne tOFF, gornja cijev se ponovo uključuje.Nakon što se gornja cijev isključi, ostat će isključena konstantno vrijeme (tOFF).tOFF je postavljen kondenzatorom (COFF) i izlaznim naponom (Vo) na periferiji kola.Ovo je prikazano na slici 2. Pošto je ILED strogo reguliran, Vo će ostati gotovo konstantan u širokom rasponu ulaznih napona i temperatura, što rezultira skoro konstantnim tOFF-om, koji se može izračunati pomoću Vo.

Slika 2. kola za kontrolu vremena isključenja i formula za izračunavanje tOFF

Slika 2. kola za kontrolu vremena isključenja i formula za izračunavanje tOFF

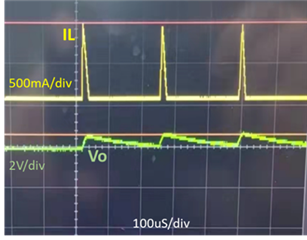

Treba napomenuti da kada odabrana metoda zatamnjivanja ili kolo zatamnjivanja zahtijeva kratki spoj, krug se u ovom trenutku neće ispravno pokrenuti.U ovom trenutku, talasanje struje induktora postaje veliko, izlazni napon postaje vrlo nizak, daleko manji od postavljenog napona.Kada dođe do ovog kvara, struja induktora će raditi s maksimalnim vremenom isključenja.Obično maksimalno vrijeme isključenja postavljeno unutar čipa dostiže 200us~300us.U ovom trenutku čini se da struja induktora i izlazni napon ulaze u režim štucanja i ne mogu normalno da izlaze.Slika 3 prikazuje abnormalni valni oblik struje induktora i izlaznog napona TPS92515-Q1 kada se šant otpornik koristi za opterećenje.

Slika 4 prikazuje tri tipa kola koja mogu uzrokovati gore navedene greške.Kada se shunt FET koristi za zatamnjivanje, šant otpornik je odabran za opterećenje, a opterećenje je LED sklopno matrično kolo, svi oni mogu kratko spojiti izlazni napon i spriječiti normalno pokretanje.

Slika 3 TPS92515-Q1 Struja induktora i izlazni napon (kratka greška izlaznog opterećenja otpornika)

Slika 3 TPS92515-Q1 Struja induktora i izlazni napon (kratka greška izlaznog opterećenja otpornika)

Slika 4. Krugovi koji mogu uzrokovati kratke spojeve na izlazu

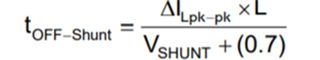

Da bi se to izbjeglo, čak i kada je izlaz kratko, potreban je dodatni napon za punjenje COFF-a.Paralelno napajanje koje se VCC/VDD može koristiti kao punjenje COFF kondenzatora, održava stabilno vrijeme isključenja i održava konstantno talasanje.Korisnici mogu rezervisati otpornik ROFF2 između VCC/VDD i COFF prilikom projektovanja kola, kao što je prikazano na slici 5, kako bi se kasnije olakšao rad na otklanjanju grešaka.U isto vrijeme, tablica sa podacima o TI čipu obično daje specifičnu formulu izračuna ROFF2 prema unutrašnjem krugu čipa kako bi se olakšao kupčev izbor otpornika.

Slika 5. SHUNT FET Eksterno kolo za poboljšanje ROFF2

Slika 5. SHUNT FET Eksterno kolo za poboljšanje ROFF2

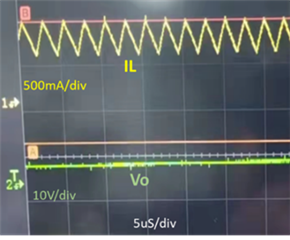

Uzimajući za primjer izlaznu grešku kratkog spoja TPS92515-Q1 na slici 3, modificirana metoda na slici 5 koristi se za dodavanje ROFF2 između VCC i COFF za punjenje COFF.

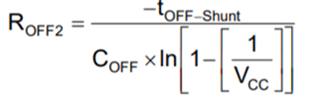

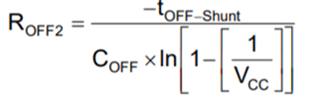

Odabir ROFF2 je proces u dva koraka.Prvi korak je izračunavanje potrebnog vremena isključivanja (tOFF-Shunt) kada se shunt otpornik koristi za izlaz, gdje je VSHUNT izlazni napon kada se shunt otpornik koristi za opterećenje.

Drugi korak je korištenje tOFF-Shunt-a za izračunavanje ROFF2, što je punjenje od VCC do COFF preko ROFF2, izračunato na sljedeći način.

Drugi korak je korištenje tOFF-Shunt-a za izračunavanje ROFF2, što je punjenje od VCC do COFF preko ROFF2, izračunato na sljedeći način.

Na osnovu proračuna, odaberite odgovarajuću vrijednost ROFF2 (50k Ohm) i povežite ROFF2 između VCC i COFF u slučaju greške na slici 3, kada je izlaz kruga normalan.Također imajte na umu da bi ROFF2 trebao biti mnogo veći od ROFF1;ako je prenizak, TPS92515-Q1 će imati problema sa minimalnim vremenom uključivanja, što će rezultirati povećanom strujom i mogućim oštećenjem čip uređaja.

Na osnovu proračuna, odaberite odgovarajuću vrijednost ROFF2 (50k Ohm) i povežite ROFF2 između VCC i COFF u slučaju greške na slici 3, kada je izlaz kruga normalan.Također imajte na umu da bi ROFF2 trebao biti mnogo veći od ROFF1;ako je prenizak, TPS92515-Q1 će imati problema sa minimalnim vremenom uključivanja, što će rezultirati povećanom strujom i mogućim oštećenjem čip uređaja.

Slika 6. Struja induktora TPS92515-Q1 i izlazni napon (normalno nakon dodavanja ROFF2)

Slika 6. Struja induktora TPS92515-Q1 i izlazni napon (normalno nakon dodavanja ROFF2)

Vrijeme objave: Feb-15-2022